Targeted subsidies for chip design companies

The scheme supports firms designing ICs, chipsets, SoCs, IP cores and related semiconductor designs. Companies with commercially deployed products can claim a payroll subsidy for Tamil Nadu residents: 30% in year one, 25% in year two, and 20% in year three, capped at ₹20,000 per employee per month. For firms that are yet to launch commercially, the State will reimburse 50% of basic payroll for three years, with a ceiling of ₹5 crore per company. An expert committee will evaluate technical viability before approval.

Prototyping delays can kill time‑to‑market. To cut this lag, the government will negotiate concessional rates with national and global fabs so that Tamil Nadu–designed chips can be fabricated faster and cheaper. The State will also promote the use of locally designed semiconductors in public procurement, within the tendering framework. This creates early demand and nudges deeper local adoption.

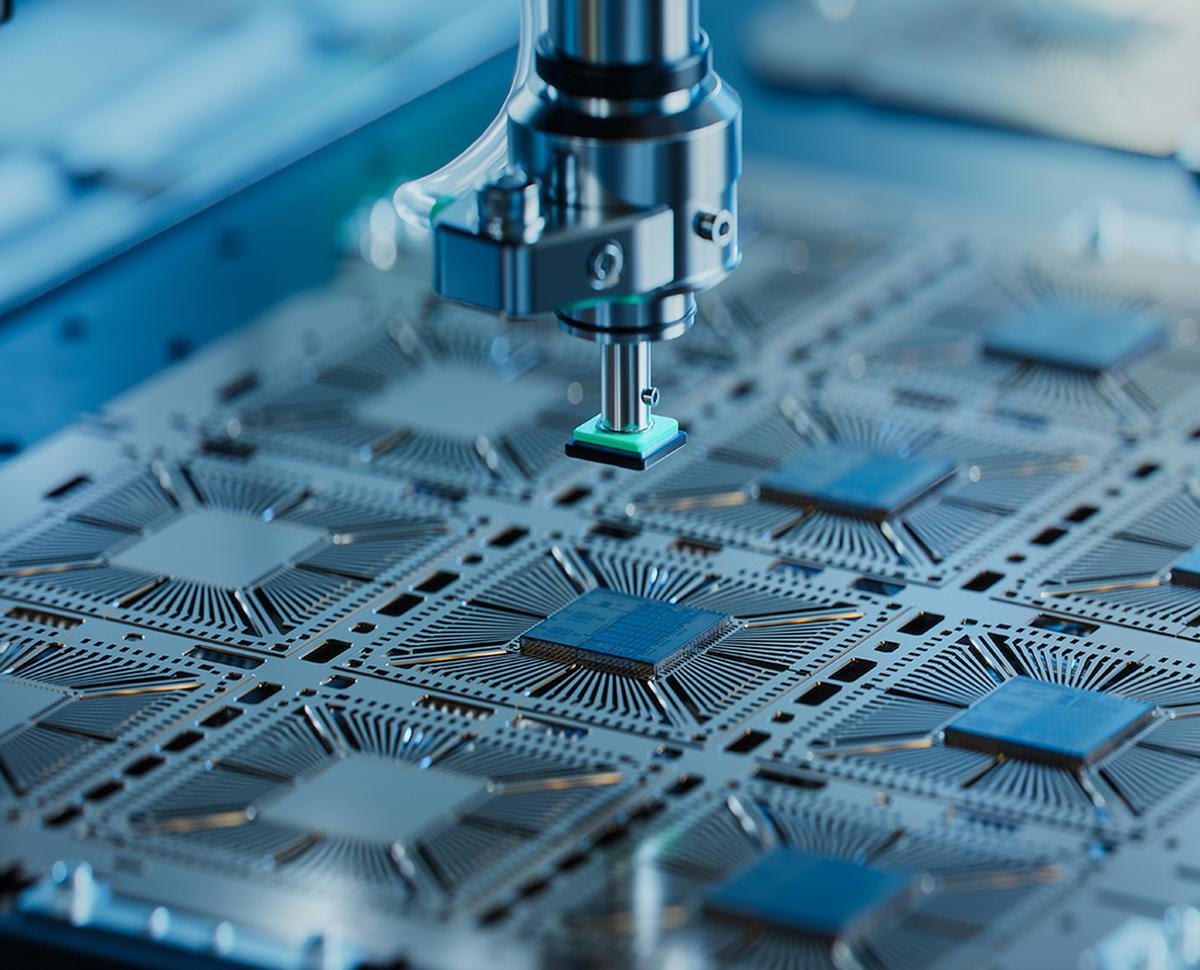

CoEs via TIDCO: shared labs, real testbeds

A network of Centres of Excellence (CoEs) will give startups and MSMEs access to EDA tools, test and validation labs, and packaging support. TIDCO will promote these CoEs through special purpose vehicles (SPVs) with private and academic partners on commercial terms. The State may provide up to 40% of project cost as a grant (capped at ₹75 crore per CoE). TIDCO can take up to 20% equity in assisted SPVs and may dilute to 5% later to bring in new investors.

Workforce: training 1,000 students under ISWDP

Talent will decide the winners. The government plans to train 1,000 engineering students under the India Semiconductor Workforce Development Program (ISWDP), which offers hands‑on learning across device physics, TCAD, and VLSI flows in partnership with academia and industry. This complements India’s central schemes that back design startups with tools and grants.

How State and Centre policies fit together

Tamil Nadu’s move fits neatly with the India Semiconductor Mission (ISM) and the Centre’s Design Linked Incentive (DLI) Scheme, which supports design across ICs, chipsets, SoCs, systems and IP cores. Startups can leverage State payroll support while tapping central design infrastructure and incentives. This stack reduces costs from concept to tape‑out and de‑risks early product cycles.

Useful links: Design Linked Incentive (ISM) | Tamil Nadu Semiconductor & Advanced Electronics Policy 2024 (PDF) | India Semiconductor Workforce Development Program (ISWDP).

Why fabless first makes sense

Chip manufacturing is capital‑intensive and slow to scale. However, fabless design can scale faster on the back of talent, EDA access, and prototyping capacity. Tamil Nadu already hosts global electronics and design centres. The new scheme builds on this base with focused subsidies, predictable procurement, and shared infrastructure. It lowers barriers for startups and encourages large firms to expand design teams in the State.

Early signals: academia‑industry collaborations

Recent announcements point to a strong research pipeline. The State has partnered with leading institutions to build advanced semiconductor technologies labs and training centres, aligning with TNSM 2030. Such centres are designed to speed up device research, enable multi‑project wafer runs, and train thousands of engineers in nanoscale design and verification tools.

What this means for founders and engineers

- Lower burn during build: Payroll support reduces early‑stage costs while teams iterate on IP and tape‑outs.

- Faster prototyping: Concessional fab access trims the cycle from design to silicon, improving investor confidence.

- Shared tools and labs: CoEs offer expensive EDA stacks and validation equipment on demand.

- Talent pipelines: ISWDP and university partnerships expand the pool of job‑ready VLSI engineers.

- Public demand signals: Preference for State‑designed chips in procurement can create reference customers.

Guardrails and what to watch

Execution will be key. Clear eligibility norms and timelines will keep approvals predictable. A transparent panel for technical viability can ensure quality. CoE pricing should stay founder‑friendly while remaining sustainable. Finally, regular dashboards on grants, outcomes, and job creation will build trust and attract more private capital.

The road ahead

Tamil Nadu’s Semiconductor Design Promotion Scheme aims to turn intent into impact. With focused subsidies, concessional prototyping, and deep skilling, the State can anchor a globally competitive fabless semiconductor ecosystem. If execution stays on track, startups could move from first silicon to scaled shipments faster. And the benefits will ripple across the value chain—from IP and EDA to testing, packaging, and advanced electronics manufacturing.